DC 参数测试:自动测试设备 (ATE) 是一种广泛用于半导体设备的测试系统,主要用于验证和确保芯片或其他电子组件的性能和可靠性。 一般场景下, ATE工程师需要将DFT提供的pattern转化为机台测试的数据格式,将DUT视为黑箱而进行地功能测试。大部分关注都集中在逻辑测试上,待测DUT是否满足其逻辑功能。然而,还有另一个同样关键的领域,那就是确保DUT的DC参数在规格范围内。如OS、PS、VIH、VIL、VOH、VOL等,这一部分恰是DFT工程师有时候不容易理解的地方。 Pin Electronics 简介 Tester PE Tester的Pin Electronics是一个非常关键的部分。它连接到DUT 的每个引脚的IO上,并负责提供各种功能来执行测试。为了能够更好地说明DC测试,简单介绍一下PE的结构和功能。

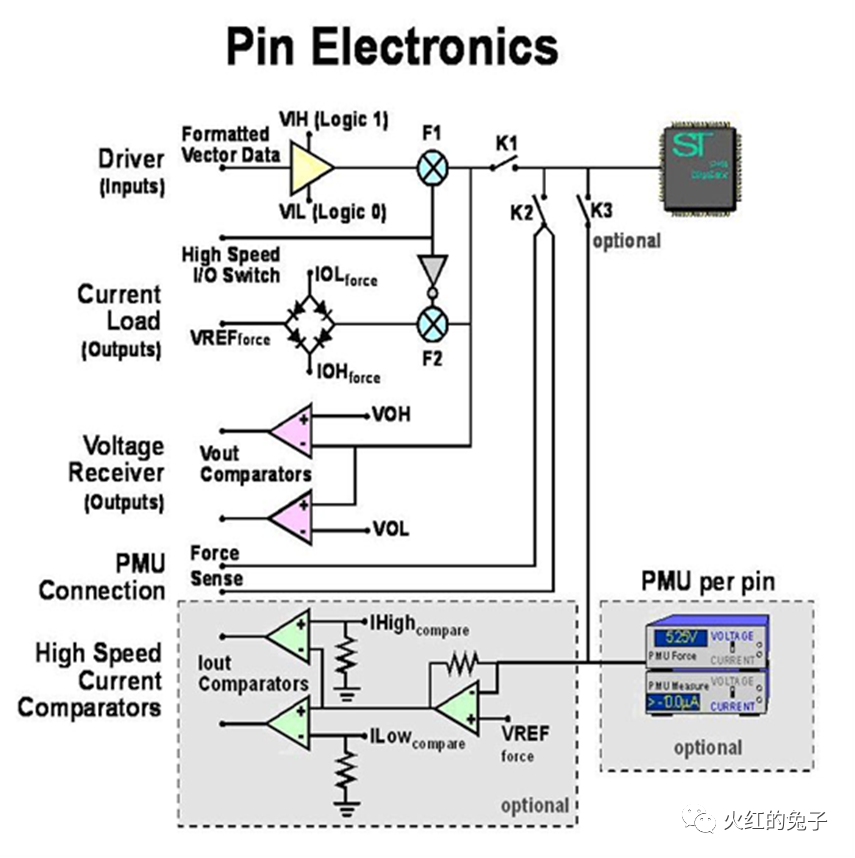

一般的PE结构可以看下图:  名词介绍

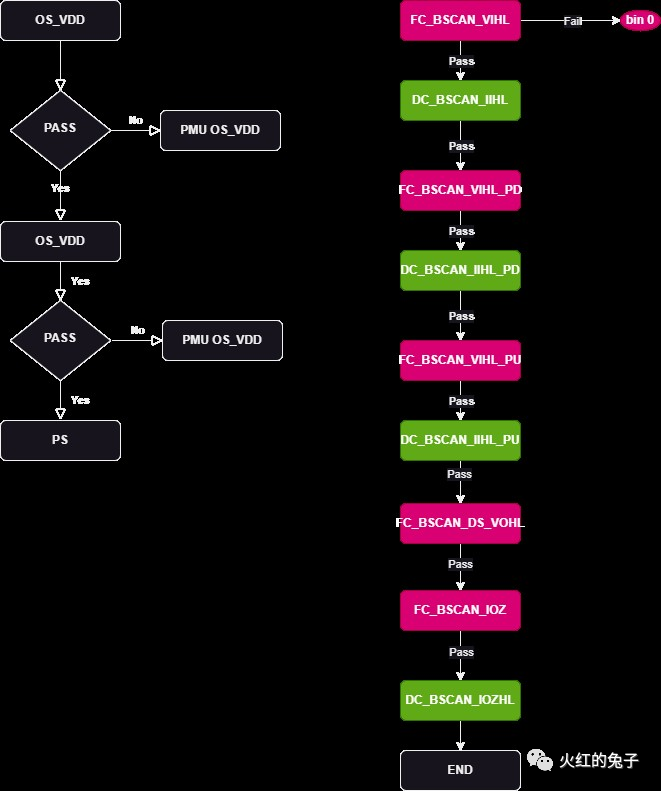

DC测试项测试那些? ATE需要创建的的DC测试项目,一般如下:  上图为一般ATE需要测试的项目: FC开头为BSCAN的pattern测试,DC开头为使用PMU进行的电流测试。 不知道各位是否注意到:没有IOHL的DC测试,WHY? 看完本篇文章后可以想一下?

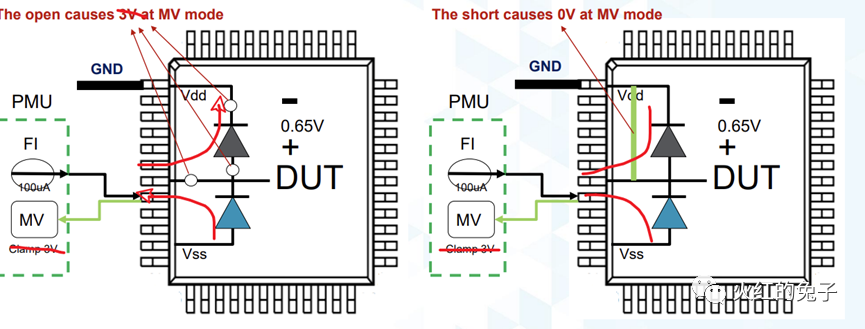

测试方法: 1. PPMU给±10uA电流模拟source和sink,分别测上下二极管的钳位电压。(参考下图的两个红色箭头方向,对应DC测试项中PMU_OS_VDD/VSS) 上二极管:0.2 < Vmeasure < 0.9V 下二极管:-0.9V < Vmeasure < -0.2V 2. 设置PE的active load,模拟±电流,跑eye matrix类型的pattern,使用阈值比较器来探测二极管导通电压。(对应DC测试项中的OS_VDD/VSS)

测试理论:欧姆定律测试方法:给电源0.1V,测电流是否过大。

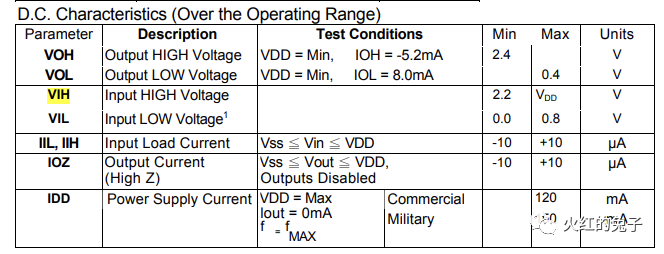

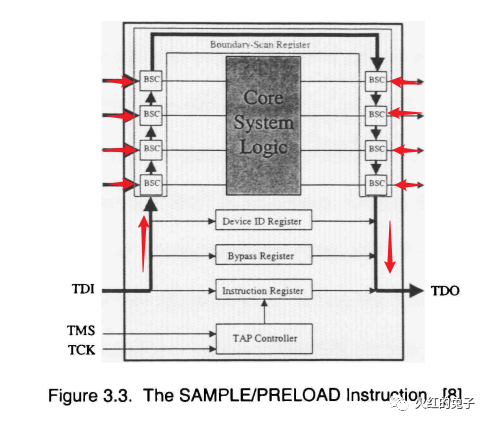

测试方法:BSCAN向量,配置IO为input状态,IO驱动高低电平,传入BSC cell,通过TDO移出比较,确定PASS/FAIL。 测试条件:VIH 选用 datasheet中的VDD MIN, VIL 选用VSS Max, 加严测试。 判断条件:向量是否PASS。

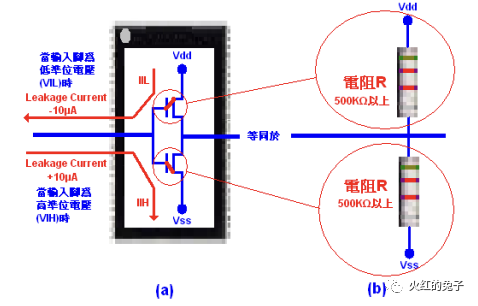

测试方法:PAD端给VDDMAX测IIH,给VSS测IIL。 测试条件:VIHL的BSCAN向量跑完后,IO处于input使能状态。 判断测试pass/fail : ±1uA

测试方法:PAD 端给VDDMAX测IIH , 给VSS测IIL。 测试条件:VIHL的BSCAN向量跑完后,IO处于input使能状态,使能上下拉 判断测试pass/fail : ±10uA

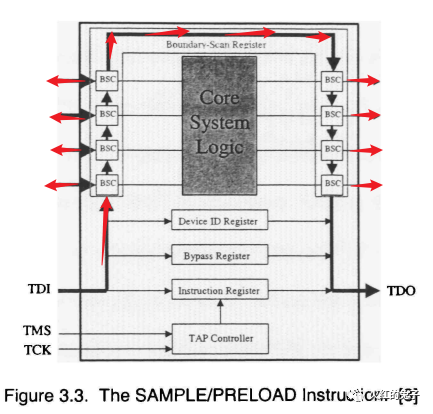

测试方法:BSCAN向量,配置IO为output状态,通过TDI传入BSC cell,再输出到IO上,比较IO的期望确定PASS/FAIL。 测试条件:VOH 选用 datasheet中的VDD MAX, VOL 选用VSS MIN, 加严测试。  注意:VOHL测试需要注意DS挡位,DS挡位配置为常用挡位,不要太低,太低时因为驱动能力弱于ACTIVE LOAD设置负载,容易引入较长的Trans delay,从而导致测试FAIL。(或ATE修改active load为极小去bypass,PASS,但可能无意义,DS挡位太低实际也不会用,最好测DUT最常用的DS挡位场景。)

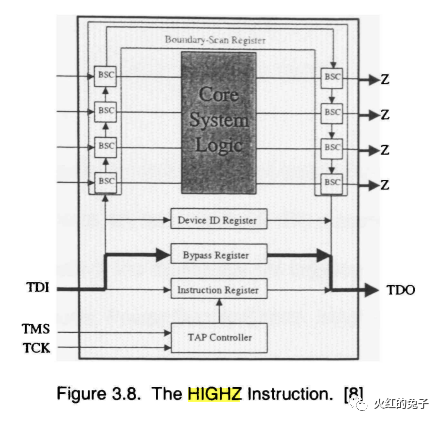

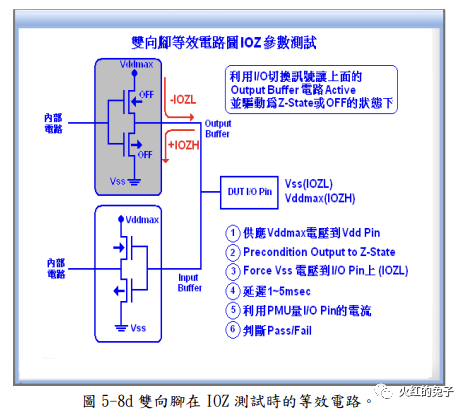

测试方法:BSCAN 向量,配置IO为高阻,比较IO的期望值是否为高阻。 判断条件:向量是否PASS。  注意:IOZ的向量测试,也可能有trans delay较大的问题,和VOHL同理。若遇到偶发性问题,可以通过更改active load设置规避。

测试方法:PAD端给VDDMAX测IOZH,给VSS测IOZL。 测试条件:VIHL的BSCAN向量跑完后,IO处于输出高阻状态。 判断测试pass/fail : ±1uA 对于双向IO,其实和IIHL差不多的道理,栅极泄漏vs亚阈值漏电。  1. The Fundamentals of Digital Semiconductor testing, Guy Perry. 2. google 3. BENEFITS OF VLSI BOUNDARY-SCAN TESTIN, EDUARDO FAVELA, B.S.E. 4.半導體測試概論 - 白安鹏 "Life is what happens to us while we are making other plans." — Allen Saunders |