|

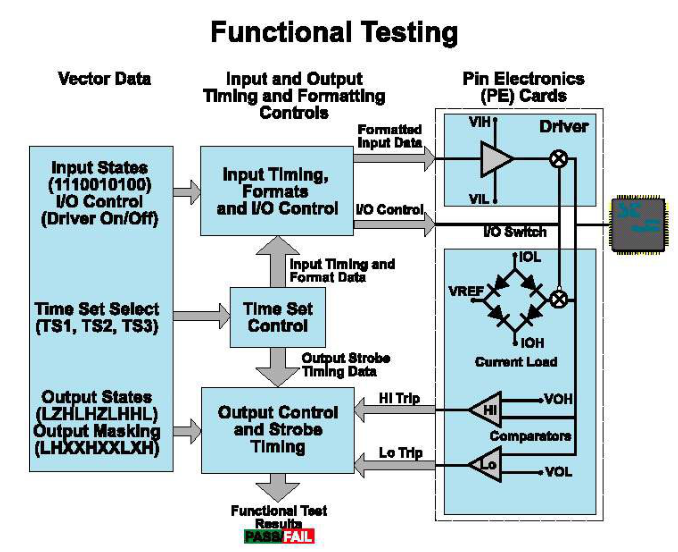

FUNCTIONAL测试原理功能测试简介功能性测试主要是验证逻辑功能。在主程序的功能测试部分中包括测试向量和相关的测试命令。其中测试向量在输入时向芯片提供逻辑状态,在输出时比较芯片的逻辑状态。在程序中的测试命令是用来控制硬件产生相应的电压、波形和时序。

图(3)

在功能测试过程中,测试系统以周期为单位将输入数据提供给芯片并比较输出数据。如果输出数据与默认的逻辑状态(测试向量的值)、电压和波形不同,则我们认为该功能测试不通过。 TestVectorTest Vector也可称为test pattern或truth table。测试向量是芯片根据设计要求而所因具有输入输出值的集合。一般用0/1来表示输入低/高电平,L/H/Z来表示输出低/高/高阻状态,X表示即无输入又无输出。并且我们可根据不同的测试系统使用不同的字符来代表不同的含义。 测试向量按在测试程序中出现的位置顺序存储在向量存储单元中,测试向量的一行表示一个测试周期。向量存储单元中的输入数据经过机台的转换变成相应的输入波形,经过PECards传给芯片。芯片的输出波形通过PECards传给机台,再由机台转变成向量,与原先存储在向量存储单元中的输出数据进行比较。 测试向量一般由设计者将仿真时的数据经过适当的转换得到,不同的机台对向量的格式有不同的要求。测试向量的总长度不可超过测试机台向量存储单元的深度。以下是一段测试向量(SC212): INPUT I/O OUTPUT 1001001111100100101 HHHHLLLLHLLL 1001001001100111011 LLLLLLLLLHHH 1001000001010101001 HLHLHLHHHLHL 1001001001011111000 LLHHLLLHHHLH 1001001111101010101 LLLLHLHLHLHL 100100HHHHLLHLHL HHHLHHLHHLHH 100100HHHLLLHLHL HHLHLHLHLHLH 100110ZZZZZZZZZZZ LHLHLHLHLHLH 100110LLHLLHLHLH HHHLHLHHLHHL

. don’t care 0 drive0 1 drive1 H compare1 L compare0 X don'tcare Z comparetri-state

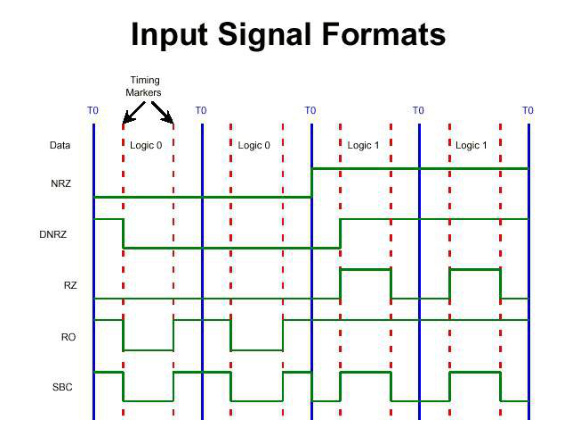

InputSignal Format

信号的波形是测试向量的重要组成部分,它保证所有的AC参数按SPEC.的要求进行测试。信号波形和向量数据、上升/下降沿的位置、输入电压值组合成输入信号波形。常见的信号波形如下图:

图(4)

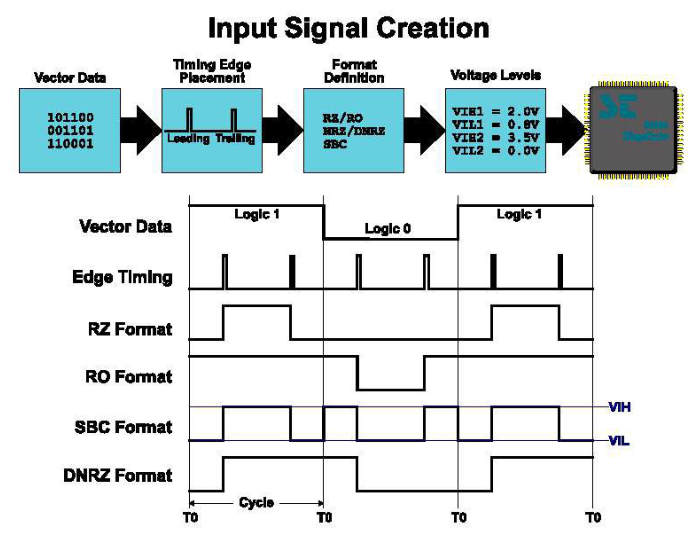

InputSignal Creation输入信号波形需要将测试系统中许多部分的数据综合起来产生,其实在测试头上看到的波形是由向量数据、EdgePlacement Timing、基本信号波形和VIL/VIH的值组合而成。如下图所示:

图(5)

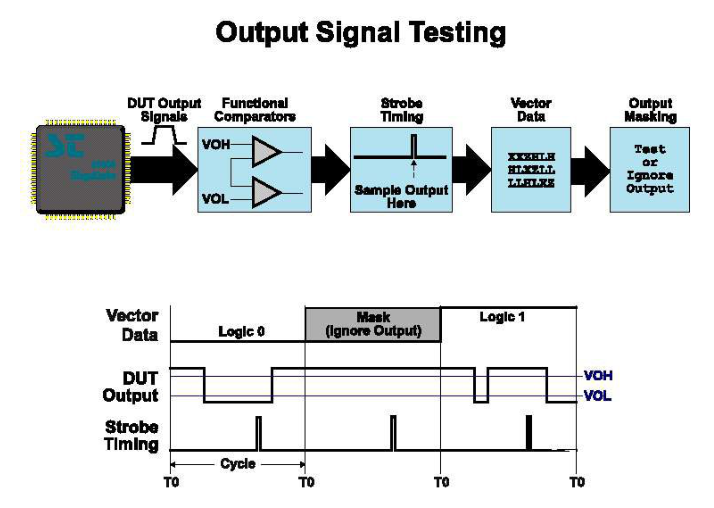

所有的输入引脚都要有相应的输入波形。时钟信号的波形一般用RZ或RO来营造,像CS(Chip Select)和READ这种高电平有效的信号用RZ来营造,而像CS/(Chip SelectBar)和OE/(OutputEnable Bar)这种低电平有效的信号用RO来营造;数据信号一般数据不定而且有SetupTime和HoldTime的要求所以用SBC来营造。其他信号一般用NRZ和DNRZ来营造。 OutputSignal Testing输出比较实际是由Test vector data(期望芯片输出的逻辑状态)、Output strobetiming(决定在测试周期中何时采样)、VOL/VOH(期望芯片输出的电压值)、IOL/IOH(期望芯片输出的电流值)四部分组成。如下图所示:

图(6)

在输出比较时,测试机台根据Strobe timing在相应的时间读取输出引脚上的电压值。如果期望输出低电平那么芯片的输出必须比设定的VOL低,如果期望输出高电平那么芯片的输出必须比设定的VOH高。并且我们可利用Output Masking来选择哪些需要进行输出比较哪些不需要,由此可形成灵活的输出比较。

|