# **D10 Application Training**

## D10 Training Outline

## Day1:

- Plateform Overview

- Timing And STIL

- Passive Load

- Instrument Pin Introduction

- Program Overview(.job, .res, .sig, user\_main, user\_load, API etc)

## Day2:

- Lab: ITE Environment

- Lab: Run the Program

- Lab: Run the Tool(shmoo, margin, pattern tool etc)

- Frequency Measurement

- To Use the DIBU

# D10 Training Outline

- Day3:

- Lab: Write your own test program (74193)

- Binning

- OIC

# D-10 Technical Overview

# Use of Existing Technology

- Use of industry standards

- STIL (Standard Tester Interface Language) Syntax

- Star Fabric cPCI bridge to backplane

- cPCI data bus interface

- Third-party cPCI and PXI instruments

- Third-party software tools

- Use of existing Credence technology

- Omni ASIC for the DPIN96

- Octet analog instruments for DMSI

- Program Developer for program generation

- Test Developer for pattern generation

- Debug tools adapted from multiple platforms

- VI technology from SZ

- RF and Power Management technology from ASL

## Architected for Performance

- Designed for multi-site

- Sites management implemented in hardware for maximum throughput and minimum overhead

- Multi-site analog and DC instruments

- D-10 software designed for multi-site

- Designed for Maximum throughput

- 250 Mbyte/s Star Fabric bridge for fast data transfers and pattern loads

- FPGA based firmware algorithms implemented to accelerate throughput

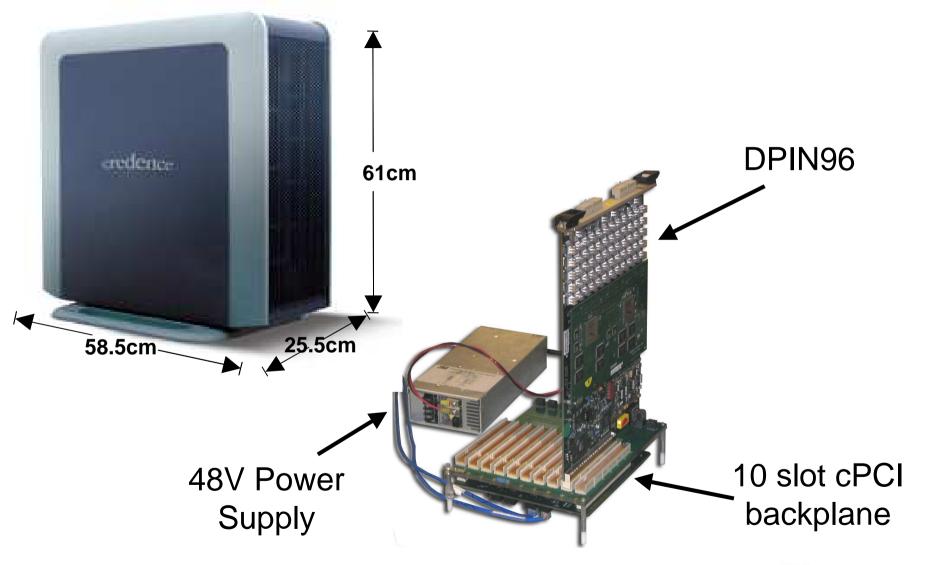

# Sapphire D-10

## D-10 Digital / MS Instruments

#### **Digital Pins**

- 96 pins, 200Mbps

- 16M parallel vector memory, reconfigurable scan

#### **Device Power**

- 16 supplies

- 0 to +6V, 2A

- Gangable to 16A

#### **VI Sources**

- 16 pins, 4 quadrant

- 20V, 300ma

- 60V, 100ma

#### **Quad M/S Instruments**

- Audio/Video AWG

- Audio/Video Digitizer

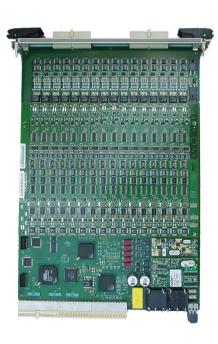

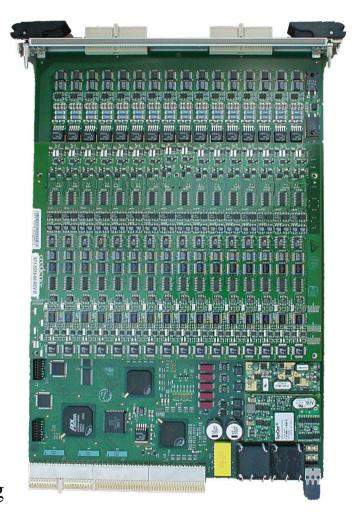

# DPIN96 Digital Pincard

| Feature           | Diamond DPIN96     |

|-------------------|--------------------|

| Channels per card | 96                 |

| Max Drv or Cmp    | 200Mbps            |

| Full Format I/O   | 200 Mbps           |

| EPA               | ±500ps             |

| Edge Resolution   | 19.5ps             |

| Rise Time         | 1.2ns @ 3V         |

| Drv Min Pulse     | 4ns @ 3V           |

| Drv / Cmp Range   | -1V to 6V          |

| Drv Super Voltage | 12V                |

| Per Pin PMU       | -2V to 12V, ± 25mA |

# DPIN96 Digital / Omni asic

| Feature           | Diamond DPIN96              |

|-------------------|-----------------------------|

| Instruction Rate  | 100 MHz                     |

| Edges per pin     | 4                           |

| Data bits per pin | 4                           |

| Time Sets:        | 256 period (global)         |

| t1 t2 t3 t4       | 256 edge per pin (global)   |

| f1 f2 f3 f4       | 256 format per pin (global) |

| Memory Depth      | 16 Meg                      |

| Scan              | Yes/Reconfigurable          |

| Fail Capture      | 64 / 16 Meg                 |

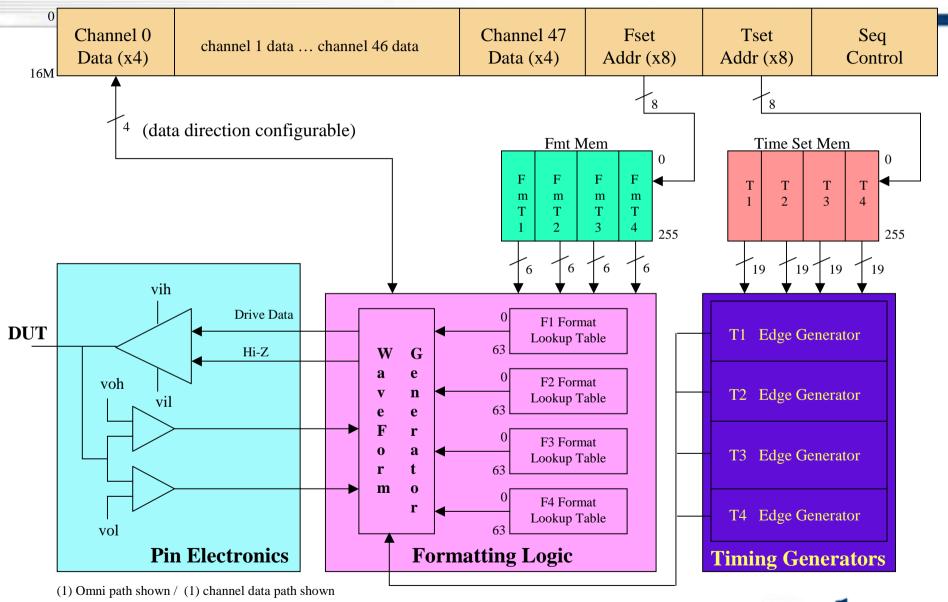

# **DPIN96** Timing

## Vector Data Flow

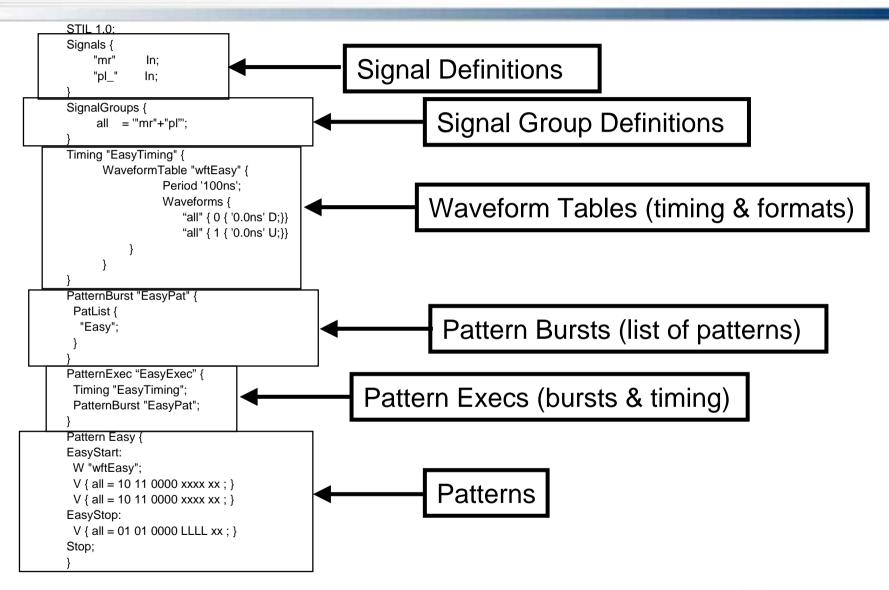

# **Timing Examples in STIL**

## The STIL File

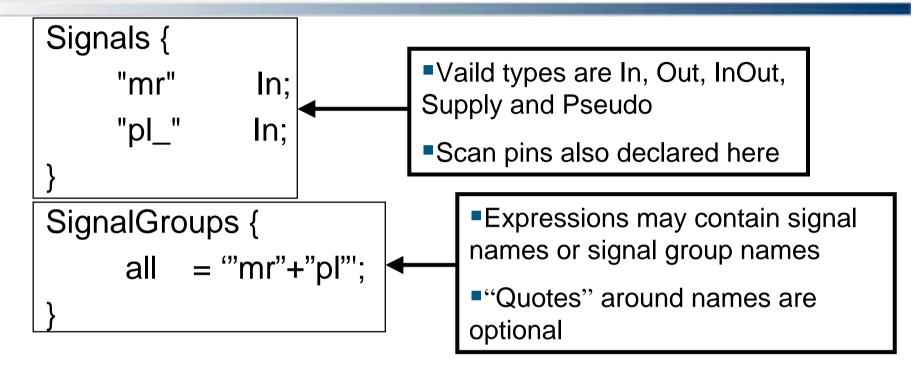

# Signals and Signal List Definitions

See the Programmer's Reference Manual or the STIL IEEE spec for more information on STIL file syntax

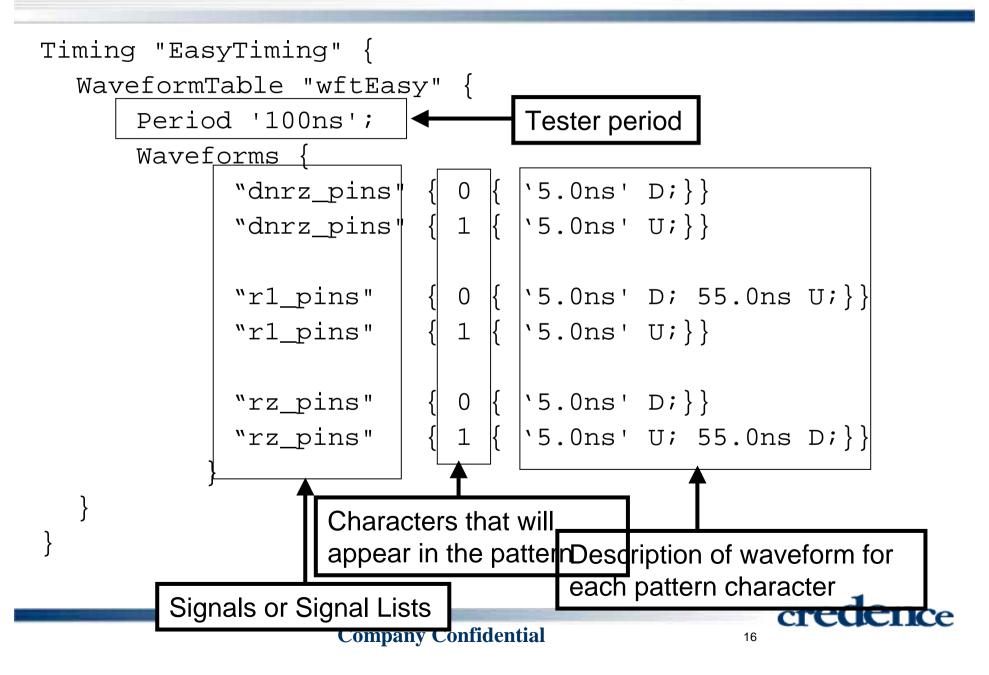

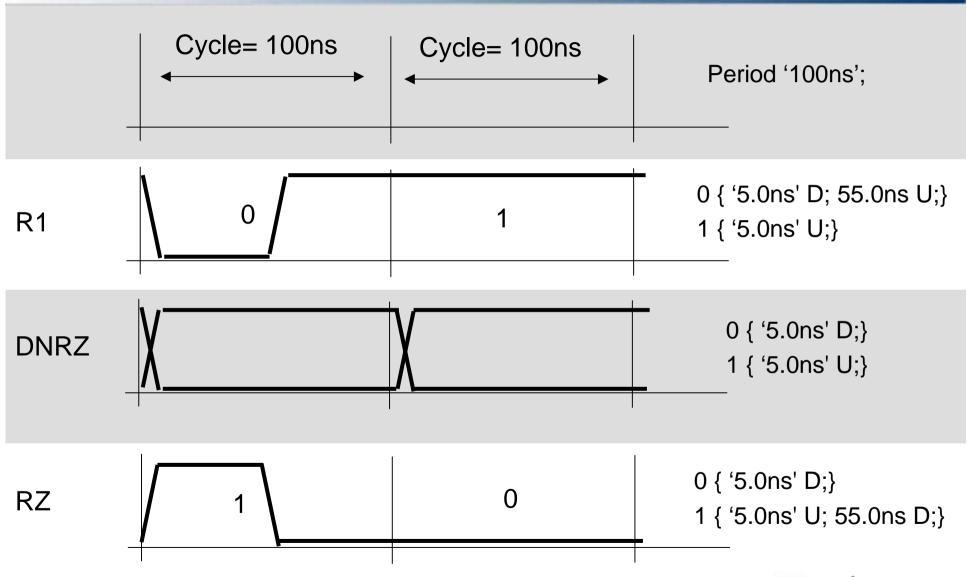

## Waveform Table Examples

# Waveforms for Timing Examples

# Four Edges Per Cycle

| Edges     | Edge 0 | Edge 1      | Edge 2          | Edge 3     |

|-----------|--------|-------------|-----------------|------------|

| Events    | X, Z   | D, U, U1, N | D, U, U1, T, V, | H, L, h, 1 |

| Allocated |        |             | t, v            |            |

- ■The D-10 STIL compiler imposes some rules on the edge formats

- If not specified by defining 'Z' for a given signal, then the inhibit edge will default to 0ns

- Pattern states are:

Z= inhibit driver X= mask

D= drive down U= drive up

T,t= compare for tristate V,v= compare for valid

H,h= compare for high L,l= compare for low

## Waveform Table Examples

```

Timing "EasyTiming" {

WaveformTable "wftEasy" {

Period '100ns';

Waveforms {

"dnrz_pins" { 0 { '5.0ns' D;}}

"dnrz_pins" { 1 { '5.0ns' U;}}

Edge2

Edge1

"r1_pins" { 0 { \ 5.0ns' D \ 55.0ns U;

"rl_pins" { 1 { '5.0ns' U; }}

"outputs" { H { '5.0ns' H;}}

"outputs" { L { '5.0ns' L;}}

Edge0

```

## The STIL File

```

PatternBurst "EasyPat" {

PatList {

Pattern Bursts (list of patterns)

"Easy";

PatternExec "EasyExec" {

Timing "EasyTiming";

Pattern Execs (bursts & timing)

PatternBurst "EasyPat";

Pattern Easy {

EasyStart:

W "wftEasy";

V \{ all = 10; \}

V \{ all = 10; \}

Patterns

EasyStop:

V \{ all = 01; \}

Stop;

```

# DPS16 Device Power Supply

- 16 source / measure channels

- Vforce:

- 0 6 V positive only

- 0.1% accuracy

- 13 bit resolution

- 2 amps per channel

- 8 channels ganged to 16 amps

- Iranges:

- 2A / 200mA / 2mA / 200uA

- 0.2% accuracy

- 16 bit resolution

- Current clamps:

- 2% accuracy

- 2A range

- Programmable / triggered 4k location cmd stack

- 64k location sample memory w/ on board averaging

## VIS16 – 4 Quadrant VI Source

- Sixteen VI source / measure channels

- Four quadrant operation in two configurations:

- ±20V @ ±300mA

- ±60V @ ±100mA

- 20V / 60V configuration programmable per channel

- Single ended voltage ranges:

- $-\pm 2V/\pm 6V/\pm 20V/\pm 60V$

- Differential voltage meas ranges (between 2 channels):

- $-\pm 20 \text{mV} / \pm 200 \text{mV} / \pm 2 \text{V} / \pm 10 \text{V}$

- Current ranges:

- $-\pm300$ nA  $/\pm3$ uA  $/\pm300$ uA  $/\pm30$ mA  $/\pm300$ mA

- ±.03% FSR accuracy / ±.01% FSR repeatability

- Programmable compensation for speed and stability

- Programmable low pass filter for measured functions

- Analog modulation up to 20kHz for PSRR tests

- Internal and external triggers for measurement sampling into 1024 location capture memory

- 50uF max capacitive load

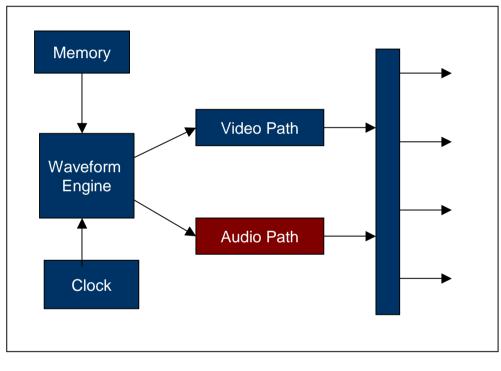

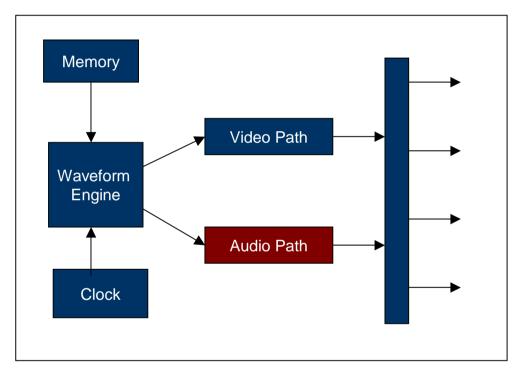

## **D-10 AWG**

**AWG**

#### Multi-Site, Multi-Band AWG

- Channels can be used single-ended or differentially

- 4 channels share the same waveform memory and the same clocking

- Offset voltage is independently adjustable

- •A high-frequency video path and a high-resolution audio path are available for each channel

## **D-10 AWG**

**AWG**

#### **Multi-Site AWG**

- Sampling rate: 300Msps

- Audio w/1KHz BPF:

THD 120dB SNR 105dB

• Video:

SNR 70dB SFDR@20MHz 70dB

#### **Instrument Clock**

• Jitter < 3ps rms

# Sapphire D-10 AWG

| Feature                     | Sapphire D-10 AWG                                           |

|-----------------------------|-------------------------------------------------------------|

| Number of outputs           | 8 SE or 4 differential                                      |

| Output impedance            | 50 Ohms                                                     |

| Output range (open circuit) | 8V p-p with ±4V common offset and ±400mV independent offset |

| Hardware resolution         | 20 bits                                                     |

| Maximum sample rate         | 300 Msps                                                    |

| Waveform memory             | 1 Megaword                                                  |

| Bandwidth (3dB typical)     | LF path: 2MHz, HF path: >100MHz                             |

# Sapphire D-10 AWG

| Feature          | Sapphire D-10 AWG                                     |

|------------------|-------------------------------------------------------|

| Jitter (typical) | 3 ps rms                                              |

| HF path filters  | 2 MHz, 6.3 MHz, 20 MHz, 63 MHz (LP, 5 pole Bessel)    |

| LF path filters  | 2 kHz, 20 kHz, 200 kHz (LP, 6 pole Bessel)            |

|                  | 1 kHz Bandpass (4 <sup>th</sup> -order Butterworth)   |

| Noise density    | 8 nV/Hz <sup>1/2</sup> (HF path, 1V p-p into 50 Ohms) |

| SFDR (including  | 85dB at 1MHz                                          |

| harmonics)       | 70dB at 20MHz                                         |

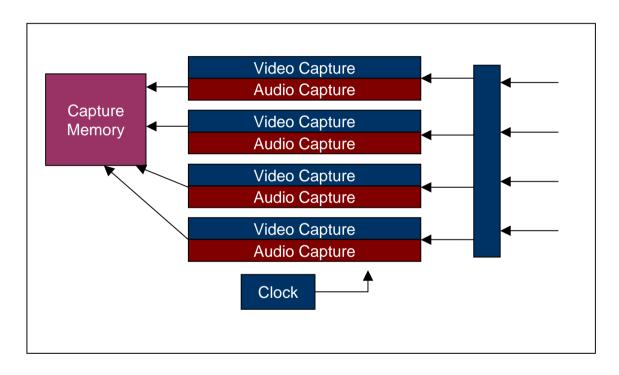

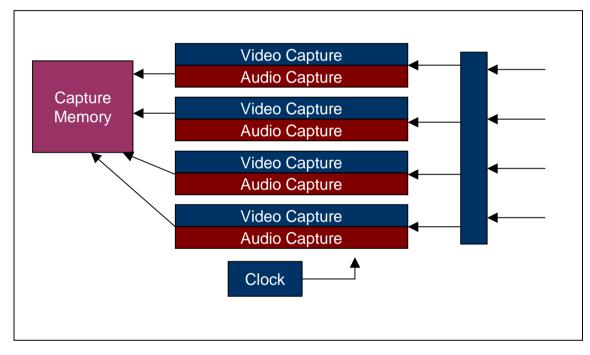

## D-10 Digitizer

#### Multi-Site, Multi-band DIG

- 4 differential input channels share the same clocking and triggering

- •A high-frequency video path and a high-resolution audio path are available for each channel

DIG

# D-10 Digitizer

**AVD**

#### Multi-Site DIG

- Sampling rate: 100Msps

- Audio w/1KHz notch:

THD 120dB

SNR 100dB

Video

SNR 68dB

SFDR@20MHz 70dB

#### **Instrument Clock**

• Jitter < 3ps rms

# Sapphire D-10 Digitizer

| Feature             | Sapphire D-10 DIG                                                                                              |

|---------------------|----------------------------------------------------------------------------------------------------------------|

| Number of channels  | 4 differential                                                                                                 |

| Input impedance     | HF: 50 or 500 Ohms (100 or 1k Ohms differential) to Vterm, programmable from –2V to +6V LF: 10 Mohm or 600 Ohm |

| Input range         | HF: 53mV to 4V (diff p-p, 2.5 dB steps) LF: 106 mV to 8 V (diff p-p, 2.5dB steps)                              |

| Maximum sample rate | 100 Msps                                                                                                       |

| Waveform memory     | 0.5 Megaword                                                                                                   |

# Sapphire D-10 Digitizer

| Feature                     | Sapphire D-10 DIG                                                                                                        |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------|

| ADC resolution              | HF: 14 bits, LF: 16 bits                                                                                                 |

| Bandwidth (3 dB typical)    | HF: 230 MHz, LF: 4 MHz                                                                                                   |

| Jitter (typical)            | 3 ps rms                                                                                                                 |

| Analog filters              | HF: 20 MHz, 63 MHz (low pass, 5 pole Bessel) LF: 63 kHz, 250 kHz (low pass, 4 pole Bessel) 1 kHz (notch with 30 dB gain) |

| Halfband decimation filters | 2x, 4x, 8x, 16x, 32x                                                                                                     |

| Noise density               | 4 nV/Hz½ (53 mV range)<br>22 nV/Hz½ (4.0 V range)                                                                        |

| SFDR (including harmonics)  | 70 dB at 20 MHz<br>(SFDR is nearly flat below 20_MHz)                                                                    |

# DIB Utility Board

- Always goes in slot 9 (last slot)

- Is required

- Fixed supplies

- Relay controls

- Communication busses

## D-10 Software

- Simple

- Intuitive

- Open-architecture

- Fast response time

- Fast runtime

- Based on

- Linux operating system

- C++ test program language

- STIL pattern format

## D-10 Software

- D-10 is committed to sharing interfaces, tools and formats with other Credence product lines as much as possible

- STIL pattern format

- Analog Wave Tool

- Program Developer

- Test Developer

- Shmoo and Margin tool

- Handler/prober interface

- Galaxy data analysis

- Datalogging formats

- Test templates

- Many more.....

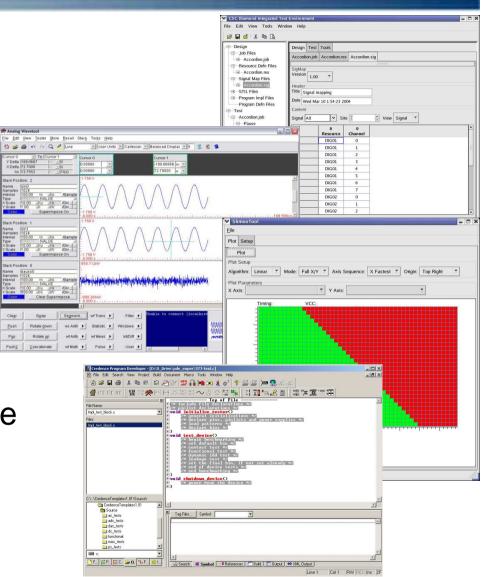

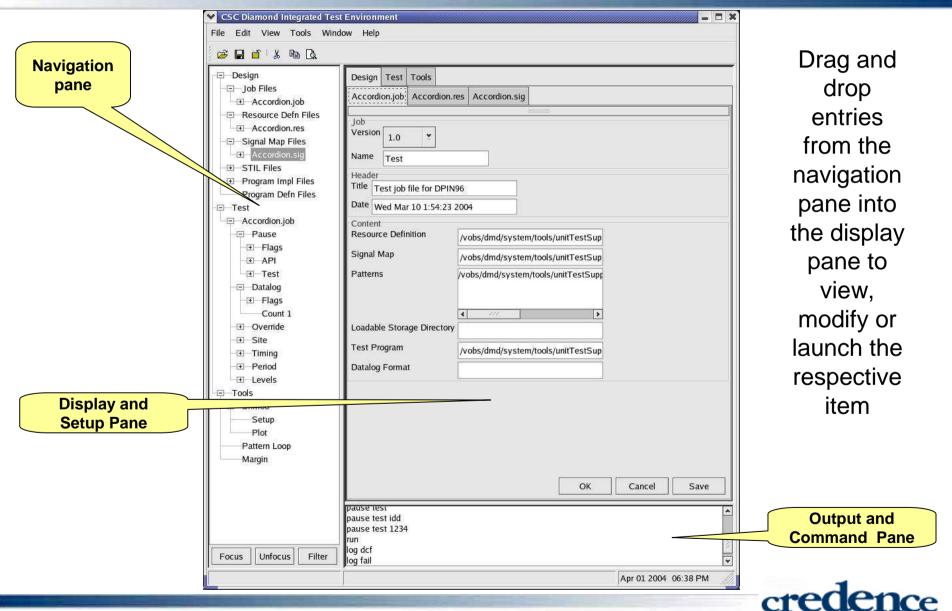

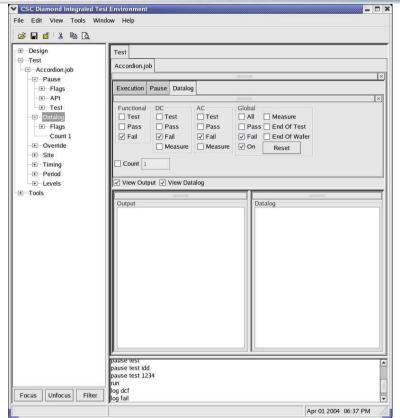

## Integrated Test Environment (ITE)

- Project overview

- Program files

- Pattern files

- Tester configuration details

- Operator interface

- Test setup

- Run control

- Datalogging

- Interactive debugging tools

- Shmoo and Margin tool

- Pattern tool

- Analog Wave Tool (AWT)

- Pin and timing status displays

- Program Developer tool

- Interactive debug commands

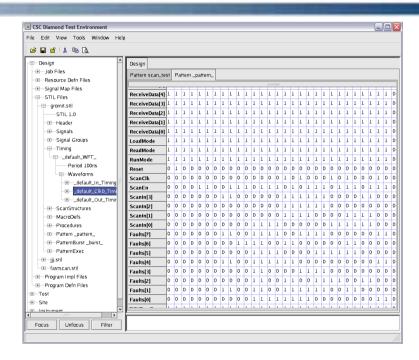

# Integrated Test Environment (ITE)

## STIL in ITE

- Pattern, signal, pinlist and timing information is automatically extracted from the STIL file

- ITE provides a graphical display and edit interface for the STIL information

## **Control Panels**

**Datalogging**

**Pausing**

Simple control panels allow the user to control the program and set parameters such as pausing and datalogging flags

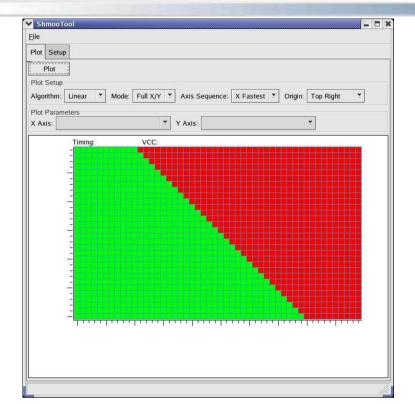

## **Debugging Tools**

**Shmoo & Margin**

**AWT**

- Dragging and dropping tools into the display pane will cause them to launch with setups for the current breakpoint

- The display pane can be undocked

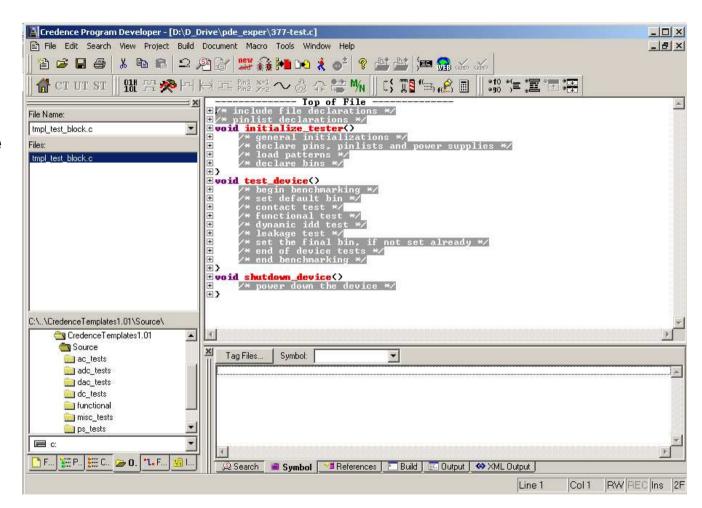

## Credence Program Developer

- Available on D-10, Sapphire and Octet

- Powerful program development and debug environment based on the SlickEdit IDE

- Browser is used to navigate directories and organize test templates supplied by Credence or written by users

- Many standard IDE features such as

- Source code debugger

- Language-sensitive editor

- Context-sensitive help

- Much, much more...

Program Developer is launched by ITE for test program development and debug

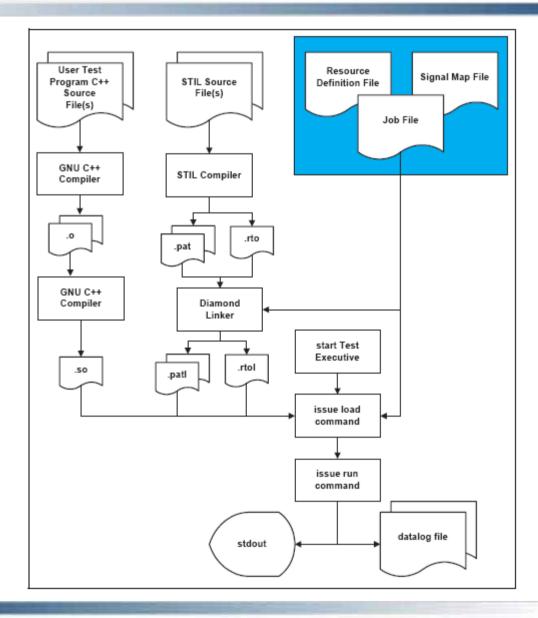

## Source Files and Job Creation

## **Passive Load**

## DPIN96

PlanetATE driver/comparator/PMU dual channel devices

Omni ASICS for timing and APG

## **DPIN96** Loads

- The DPIN96 has programmable loads per pin

- Loads consist of termination voltage connected through a resistive load

- The value of the resistive load is selected from a list of 8 possible values

- The termination voltage is programmable on a per-pin basis across the range of -1.5V to 12V

- Using the Ohm's Law, the proper values can be chosen to achieve the desired load current

- Both Ioh and Iol can be tested by running a 2-pass functional test with the loads set to the respective load currents for each pass

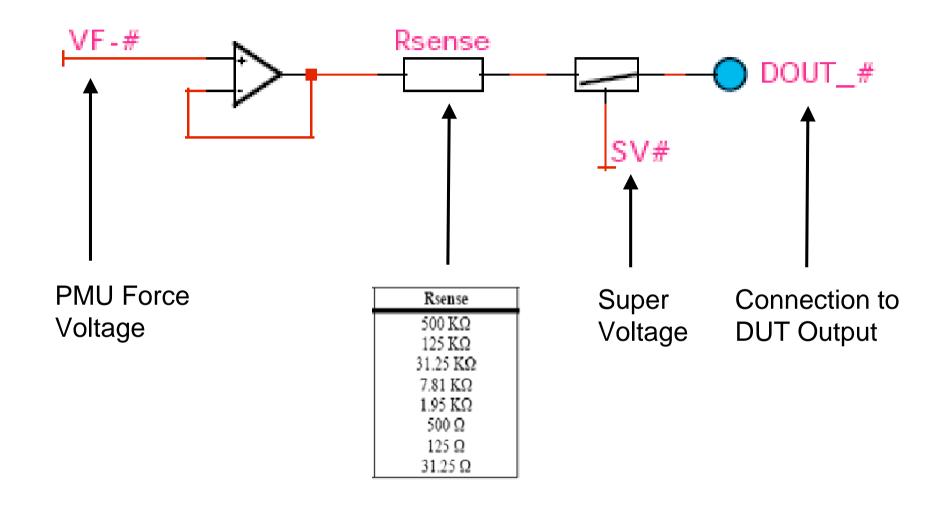

## Static Load Circuit

# Force and Measure Current Ranges

| Current Range | Imax   | Rsense           |

|---------------|--------|------------------|

| IR0           | 2 μΑ   | 500 <b>K</b> Ω   |

| IR1           | 8 μΑ   | 125 <b>K</b> Ω   |

| IR2           | 32 μΑ  | 31.25 <b>K</b> Ω |

| IR3           | 128 μΑ | 7.81 KΩ          |

| IR4           | 512 μA | 1.95 KΩ          |

| IR5           | 2 mA   | 500 Ω            |

| IR6           | 8 mA   | 125 Ω            |

| IR7           | 32 mA  | 31.25 Ω          |